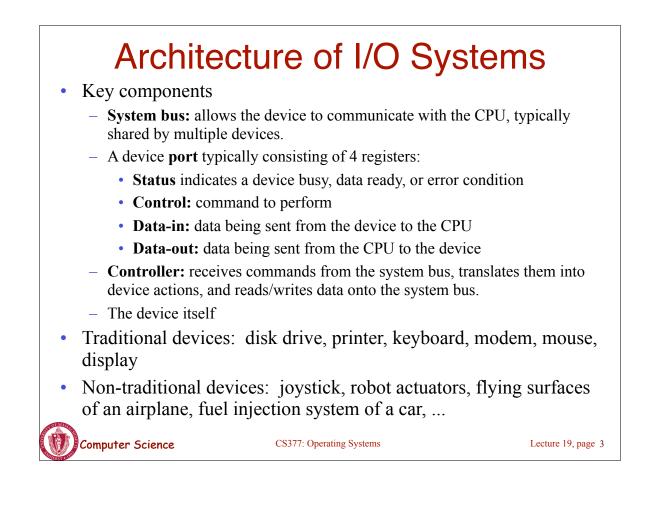

# Today: I/O Systems

- How does I/O hardware influence the OS?

- What I/O services does the OS provide?

- How does the OS implement those services?

- How can the OS improve the performance of I/O?

### Kernel I/O Subsystem

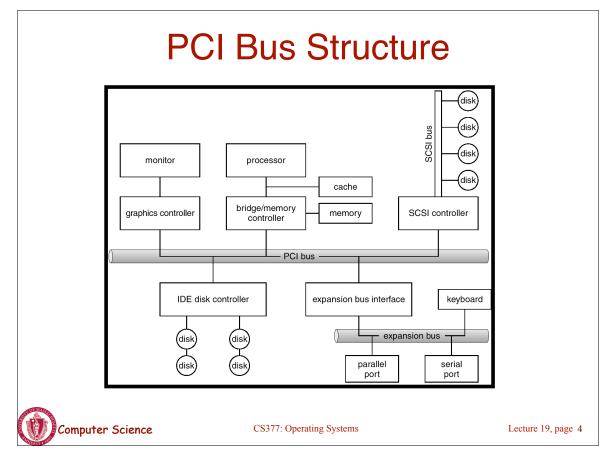

#### **Device I/O Port location on PCs**

| I/O address range (hexadecimal) | device                    |  |

|---------------------------------|---------------------------|--|

| 000-00F                         | DMA controller            |  |

| 020-021                         | interrupt controller      |  |

| 040-043                         | timer                     |  |

| 200-20F                         | game controller           |  |

| 2F8-2FF                         | serial port (secondary)   |  |

| 320-32F                         | hard-disk controller      |  |

| 378-37F                         | parallel port             |  |

| 3D0-3DF                         | graphics controller       |  |

| 3F0-3F7                         | diskette-drive controller |  |

| 3F8-3FF                         | serial port (primary)     |  |

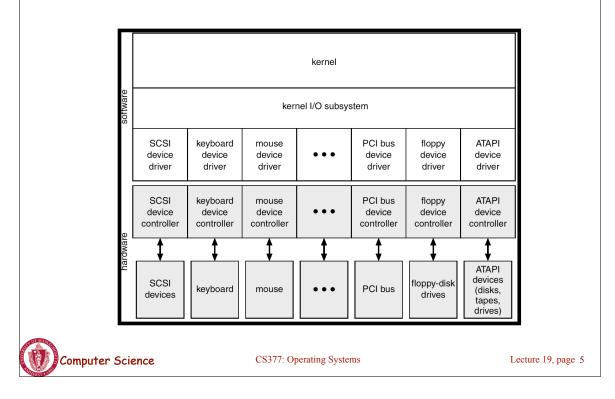

## I/O Services Provided by OS

- Naming of files and devices. (On Unix, devices appear as files in the /dev directory)

- Access control.

- Operations appropriate to the files and devices.

- Device allocation.

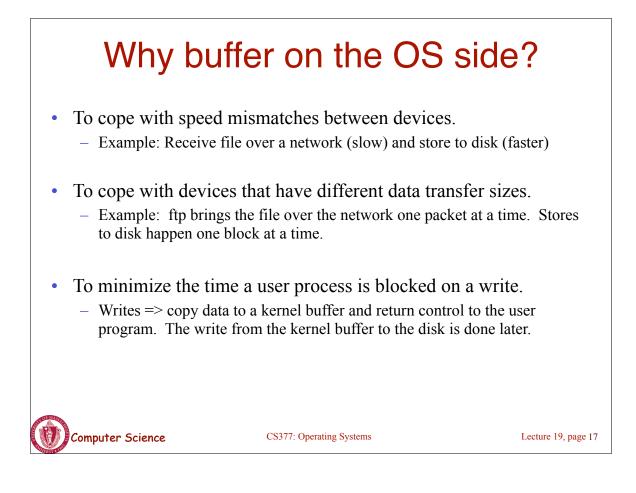

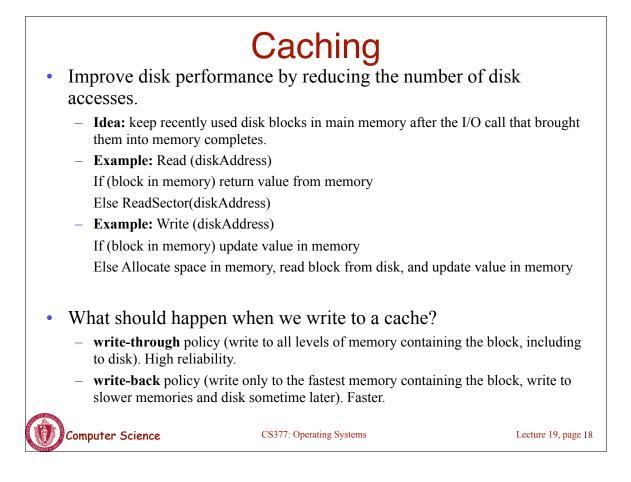

- Buffering, caching, and spooling to allow efficient communication with devices.

- I/O scheduling.

- Error handling and failure recovery associated with devices (command retries, for example).

- Device drivers to implement device-specific behaviors.

```

Computer Science

```

**Communication using Polling**

CS377: Operating Systems

- CPU busy-waits until the status is idle.

- CPU sets the command register and data-out if it is an output operation.

- CPU sets status to command-ready => controller sets status to busy.

- Controller reads the command register and performs the command, placing a value in data-in if it is an input command.

- If the operation succeeds, the controller changes the status to idle.

- CPU observes the change to idle and reads the data if it was an input operation.

- Good choice if data must be handled promptly, like for a modem or keyboard.

- What happens if the device is slow compared to the CPU?

Lecture 19, page 7

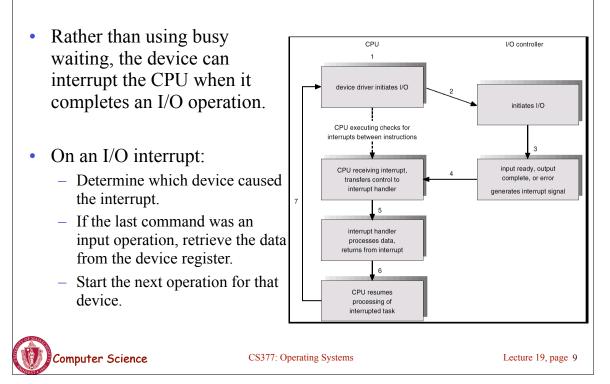

## **Communication using Interrupts**

#### Intel x86 Event Vectors

| vector number | description                            |  |

|---------------|----------------------------------------|--|

| 0             | divide error                           |  |

| 1             | debug exception                        |  |

| 2             | null interrupt                         |  |

| 3             | breakpoint                             |  |

| 4             | INTO-detected overflow                 |  |

| 5             | bound range exception                  |  |

| 6             | invalid opcode                         |  |

| 7             | device not available                   |  |

| 8             | double fault                           |  |

| 9             | coprocessor segment overrun (reserved) |  |

| 10            | invalid task state segment             |  |

| 11            | segment not present                    |  |

| 12            | stack fault                            |  |

| 13            | general protection                     |  |

| 14            | page fault                             |  |

| 15            | (Intel reserved, do not use)           |  |

| 16            | floating-point error                   |  |

| 17            | alignment check                        |  |

| 18            | machine check                          |  |

| 19Đ31         | (Intel reserved, do not use)           |  |

| 32Ð255        | maskable interrupts                    |  |

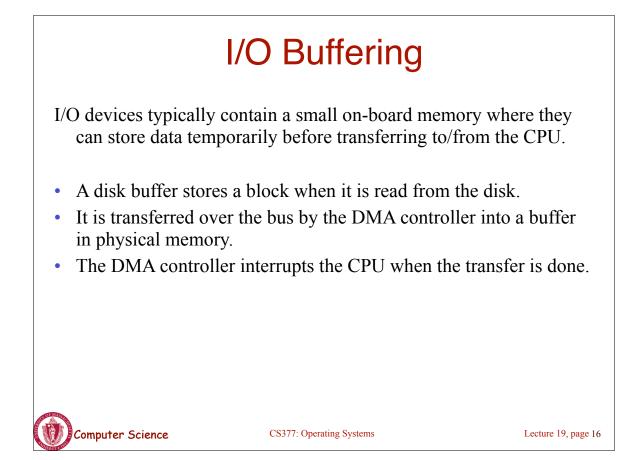

### **Direct Memory Access**

- For devices that transfer large volumes of data at a time (like a disk block), it is expensive to have the CPU retrieve these one byte at a time.

- Solution: Direct memory access (DMA)

- Use a sophisticated DMA controller that can write directly to memory. Instead of data-in/data-out registers, it has an address register.

- The CPU tells the DMA the locations of the source and destination of the transfer.

- The DMA controller operates the bus and interrupts the CPU when the entire transfer is complete, instead of when each byte is ready.

CS377: Operating Systems

The DMA controller and the CPU compete for the memory bus, slowing down the CPU somewhat, but still providing better performance than if the CPU had to do the transfer itself.

Lecture 19, page 11

Steps in DMA transfer 1. device driver is told to transfer disk data to CPU buffer at address X 5. DMA controller transfers 2 device driver tells disk controller to transfer C bytes to buffer X. increasing memory bytes from disk to buffer cache address and decreasing at address X C until C = 0when C = 0, DMA DMA/bus/interrupt buffer CPU memory bus memory interrupts CPU to signal controller transfer completion PCI bus 3. disk controller initiates DMA transfer IDE disk controller 4. disk controller sends each byte to DMA controller dis omputer Science CS377: Operating Systems Lecture 19, page 12

#### Application Programmer's View of I/O Devices The OS provides a high-level interface to devices, greatly simplifying the • programmer's job. - Standard interfaces are provided for related devices. - Device dependencies are encapsulated in device drivers. New devices can be supported by providing a new device driver. **Device characteristics:** Transfer unit: character or block - Access method: sequential or random access Timing: synchronous or asynchronous • Most devices are asynchronous, while I/O system calls are synchronous => The OS implements blocking I/O Sharable or dedicated Speed Operations: Input, output, or both Examples: keyboard (sequential, character), disk (block, random or sequential) CS377: Operating Systems Computer Science Lecture 19, page 13

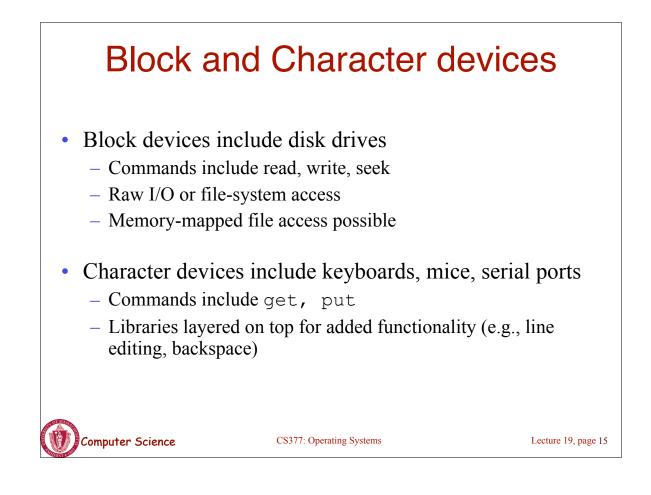

### Examples of I/O Device types

| aspect             | variation                                                         | example                               |

|--------------------|-------------------------------------------------------------------|---------------------------------------|

| data-transfer mode | character<br>block                                                | terminal<br>disk                      |

| access method      | sequential random                                                 | modem<br>CD-ROM                       |

| transfer schedule  | synchronous<br>asynchronous                                       | tape<br>keyboard                      |

| sharing            | dedicated<br>sharable                                             | tape<br>keyboard                      |

| device speed       | latency<br>seek time<br>transfer rate<br>delay between operations |                                       |

| I/O direction      | read only<br>write only<br>readĐwrite                             | CD-ROM<br>graphics controller<br>disk |

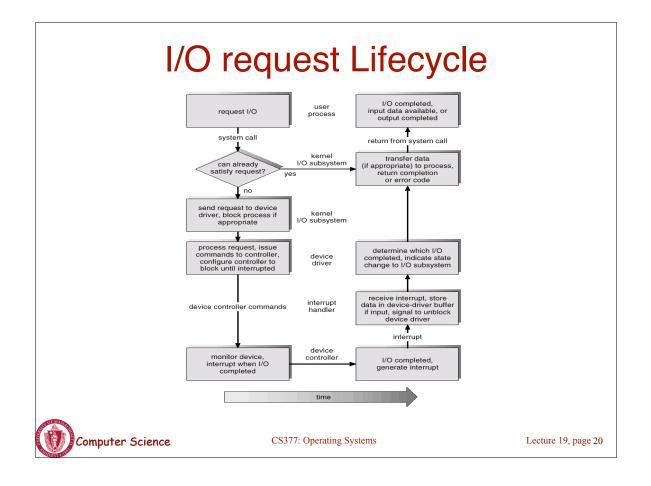

#### Putting the Pieces Together - a Typical Read Call

- 1. User process requests a read from a device.

- 2. OS checks if data is in a buffer. If not,

- a) OS tells the device driver to perform input.

- b) Device driver tells the DMA controller what to do and blocks itself.

- c) DMA controller transfers the data to the kernel buffer when it has all been retrieved from the device.

Lecture 19, page 19

- d) DMA controller interrupts the CPU when the transfer is complete.

- 3. OS transfers the data to the user process and places the process in the ready queue.

- 4. When the process gets the CPU, it begins execution following the system call.

#### Summary I/O is expensive for several reasons: • - Slow devices and slow communication links - Contention from multiple processes. - I/O is typically supported via system calls and interrupt handling, which are slow. Approaches to improving performance: • - Reduce data copying by caching in memory - Reduce interrupt frequency by using large data transfers - Offload computation from the main CPU by using DMA controllers. Increase the number of devices to reduce contention for a single device and thereby improve CPU utilization. Increase physical memory to reduce amount of time paging and thereby improve CPU utilization. Lecture 19, page 21 **Computer Science** CS377: Operating Systems